Hochschule für Angewandte Wissenschaften Hamburg Hamburg University of Applied Sciences

# Abstract

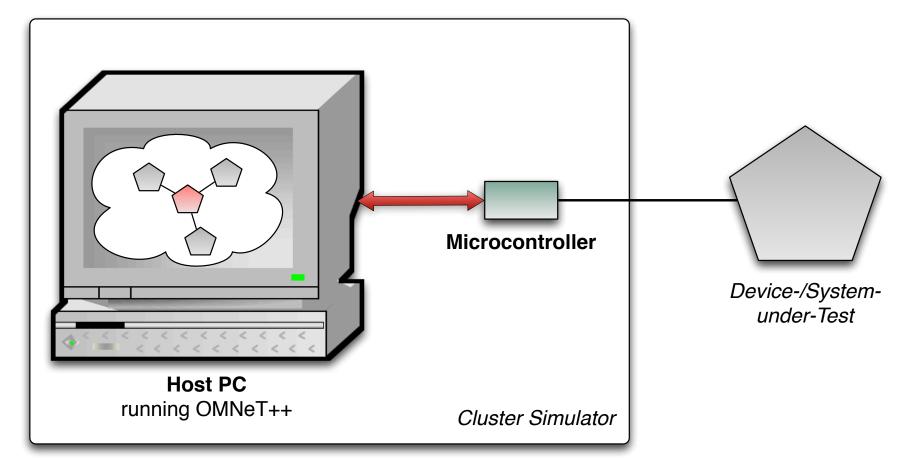

Cluster simulation is a popular method for supporting system integration in various distributed applications by simulating the environment of a subsystem under test. We contribute a scheme for cluster simulation of realtime Ethernet (RTEthernet) based distributed systems. It relies on the discrete event-based simulation framework OMNeT++, interconnected with an ARM-based co-processor. The results show that the timing requirements for the cluster simulation of small RTEthernet networks can be achieved.

# Introduction & Motivation

- Software simulation of distributed real-time systems is established for design and reconfiguration phases

- Cluster simulation is useful by simulating not available hardware during integration and setup phases

- Environments for cluster simulation generally use dedicated and expensive real-time hardware platforms

- These platforms are inflexible and specifically designed for one use-case and do not allow modifications of the network protocol itself

# Background

- A cluster simulator is only connected to the systemunder-test (SUT) via the communication interface and is triggered with regular data frames

- Behavior verification of the SUT is possible on the abstract data level by analyzing the received frames

- TTEthernet [3] is a RTEthernet implementation that classifies the traffic into time-triggered (TT), rateconstrained (RC) and best-effort (BE) messages

- A fail-safe time synchronisation protocol accomplishes the required system wide time base for time-triggered transmission

6th Int. Workshop on OMNeT++ March 5th, 2013 – Cannes

# A Hardware/Software Platform for **Real-time Ethernet Cluster Simulation in OMNeT++**

Oleg Karfich, Florian Bartols, Till Steinbach, Franz Korf, Thomas C. Schmidt Hamburg University of Applied Sciences Faculty of Engineering & Computer Science, Department of Computer Science

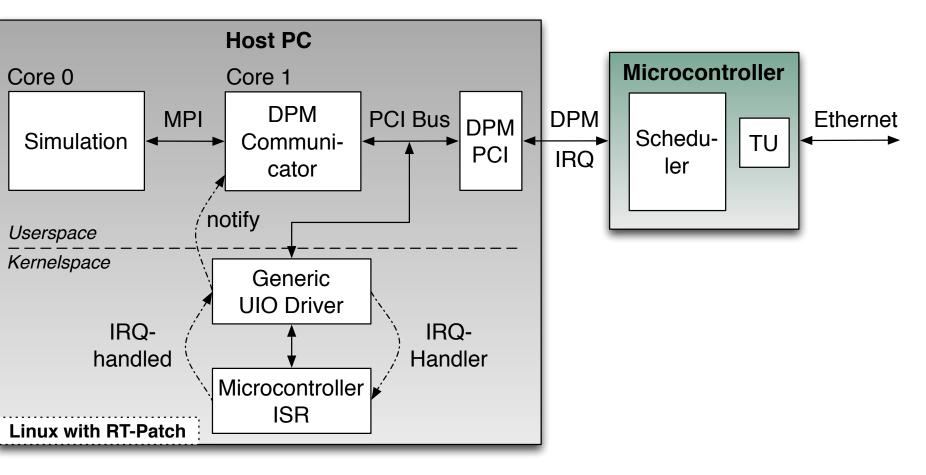

# Concept

Implementation

• Virtual dual port memory (DPM) connects the host with • The Linux network stack does not fulfill the timing requirements for precise frame transmission and recepthe microcontroller tion in the lower microseconds range • The simulation environment is separated on two dedicated CPU cores that communicate via the Message • Sending frames is accomplished with the high-resolution scheduler of the microcontroller Passing Interface (MPI) • To minimise latency and jitter the Linux real-time Ker-• The reception of frames in the simulation has to be prioritised due the TTEthernet message classes nel patch is utilised

Measurement Results

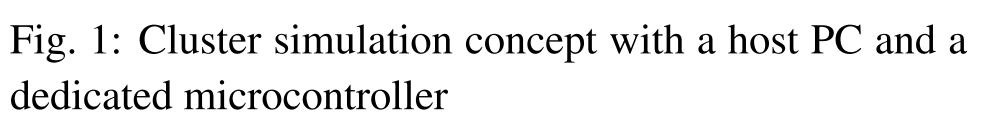

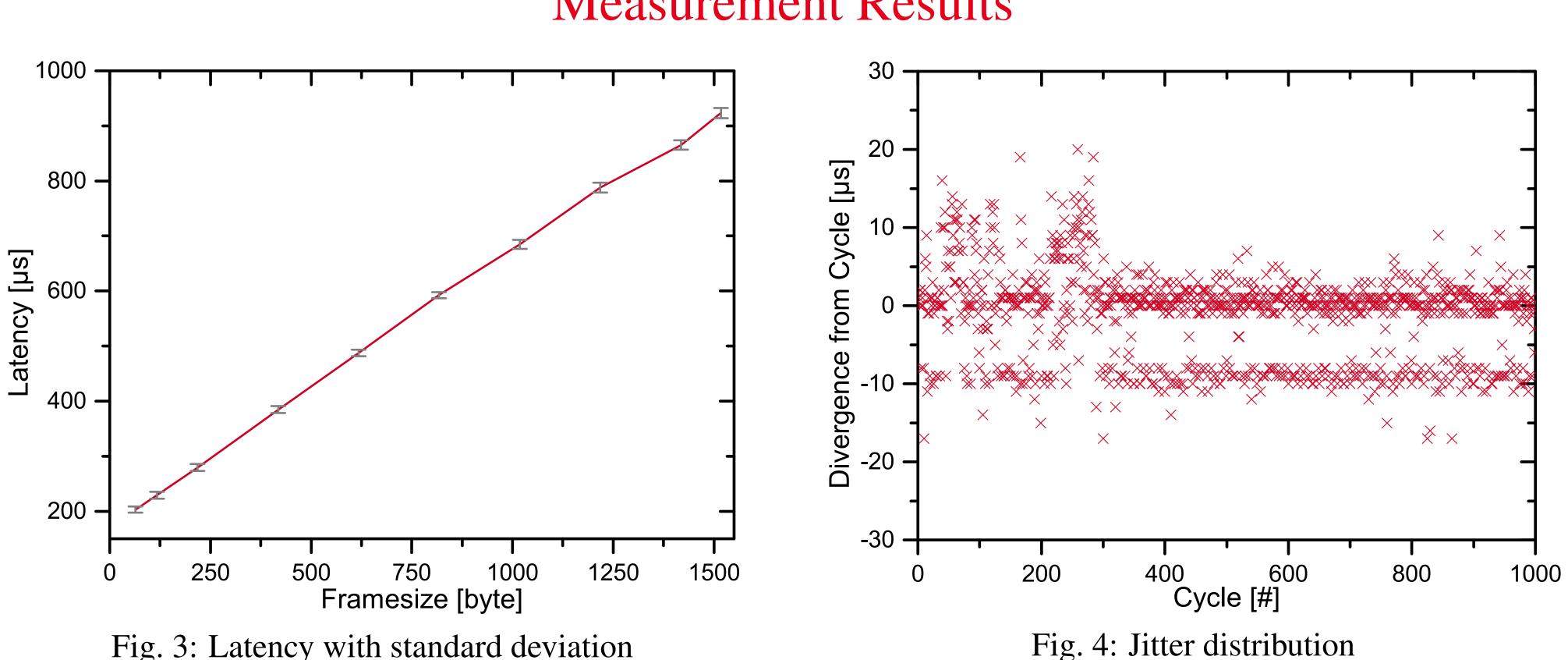

Fig. 3: Latency with standard deviation

**Contact:** {oleg.karfich, florian.bartols, till.steinbach, korf, schmidt}@informatik.haw-hamburg.de – Hamburg University of Applied Sciences, Department of Computer Science, Berliner Tor 7, D-20099 Hamburg – Web: http://www.haw-hamburg.de/core Acknowledgement: This work is funded by the Federal Ministry of Education and Research of Germany (BMBF) within the RECBAR project.

# Architecture

Fig. 2: Architecture with virtual dual port memory and the Message Passing Interface

- the jitter

- 2011. IEEE Press.

## Discussion of Results

• The latency of the frame reception from the real network to the simulation is linear, dependent on the frame size and has a static part of 186.4 µs

• Jitter analysis shows that incoming TT-messages have a maximum of 37 µs which is caused by the host system due to the used off-the-shelf hardware

• Applications that have latency requirements up to 230 µs can be simulated with our approach

### Outlook

• The microcontroller is planned to be replaced by a special network interface card with a hardware time stamping unit and a higher bandwidth

• A further investigation on how the simulation can benefit from multicore parallelisation will be applied

• The utilised real-time Kernel patch and other Linux real-time approaches will be deeper analysed to reduce

### References

[1] J. Juárez, C. Rodríguez-Morcillo, and J. A. Rodríguez-Mondéjar. Simulation of IEC 61850-based substations under OMNeT++. In Proc. of the 5th Int. ICST Conf. on Simulation Tools and Techniques, pages 319–326, New York, Mar. 2012. ACM-DL. 2] K. Müller, T. Steinbach, F. Korf, and T. C. Schmidt. A Real-time Ethernet Prototype Platform for Automotive Applications. In 2011 IEEE Int. Conf. on Consumer Electronics - Berlin (ICCE-Berlin), pages 221-225, Piscataway, New Jersey, Sept.

[3] SAE. Time-Triggered Ethernet AS6802. SAE Aerospace, Nov. 2011.

[4] T. Steinbach, H. Dieumo Kenfack, F. Korf, and T. C. Schmidt. An Extension of the OMNeT++ INET Framework for Simulating Real-time Ethernet with High Accuracy. In Proc. of the 4th Int. ICST Conf. on Simulation Tools and Techniques, pages 375–382, New York, Mar. 2011. ACM-DL.

[5] M. Tüxen, I. Rüngeler, and E. P. Rathgeb. Interface Connecting the INET Simulation Framework with the Real World. In Proc. of the 1st Int. Conf. on Simulation Tools and Techniques for Communications, Networks and Systems & Workshops, pages 40:1-40:6, New York, Mar. 2008. ACM-DL.

Federal Ministry of Education and Research